CoWoS 封装 | CoWoS-S / CoWoS-R / CoWoS-L

……

注:本文为 “CoWoS 封装” 相关合辑。

英文引文,机翻未校。

中文引文,略作重排,未整理去重。

图片清晰度受引文原图所限。

如有内容异常,请看原文。

CoWoS®-S

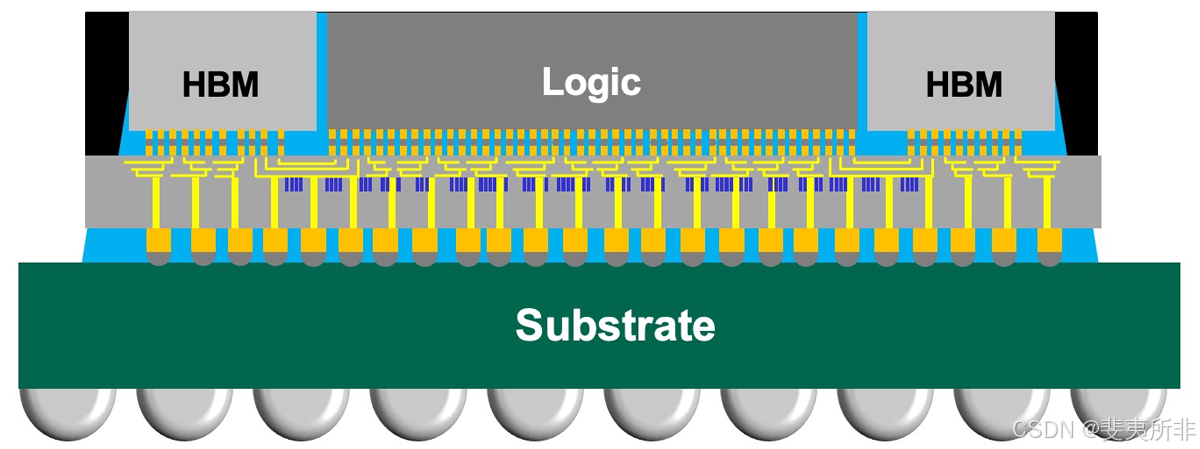

The CoWoS®-S (Chip on Wafer on Substrate with silicon interposer) platform provides best-in-class package technology for ultra-high performance computing applications, such as artificial intelligence (AI) and super-computing. This wafer level system integration platform offers high density interconnects and deep trench capacitors over a large silicon interposer area to accommodate various functional top die/dice, including logic chiplets, with High Bandwidth Memory (HBM) cubes stacked over it. Currently, an interposer up to 3.3X-reticle size (or ~2700mm²) is ready for production. The CoWoS®-L and CoWoS®-R platform are recommended for larger than 3.3X-reticle interposer sizes. Different interconnect options provide more flexibility integration to meet performance targets.

CoWoS-S®(带硅中介层的衬底晶圆上芯片)平台为人工智能(AI)和超级计算等超高性能计算应用提供一流的封装技术。该晶圆级系统集成平台在较大的硅中介层区域上提供高密度互连和深沟槽电容器,以容纳各种功能性顶部晶片/晶片,包括逻辑小芯片,并在其上堆叠了高带宽内存(HBM)立方体。目前,最大 3.3 倍掩模尺寸(或 ~2700mm²)的中介层已准备好投入生产。对于大于 3.3X 标线尺寸的内插器,建议使用 CoWoS-L® 和 CoWoS-R® 平台。不同的互连选项提供了更大的集成灵活性,以满足性能目标。

CoWoS®-R

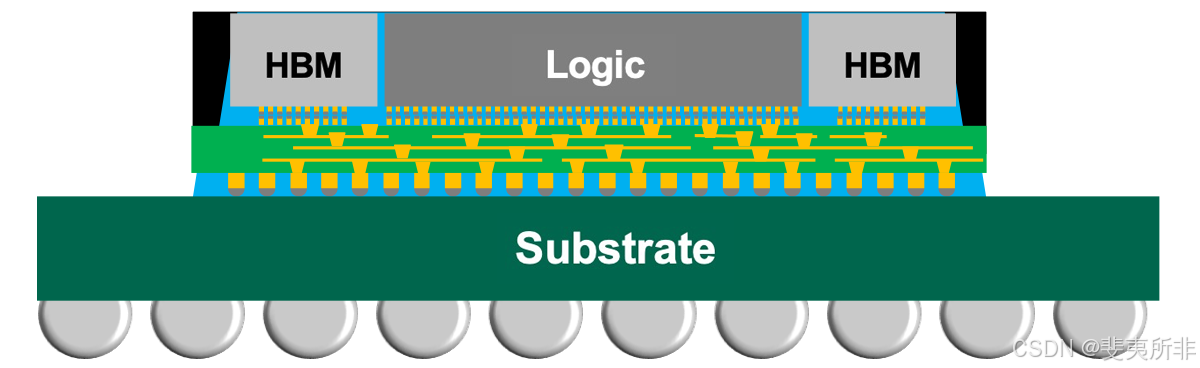

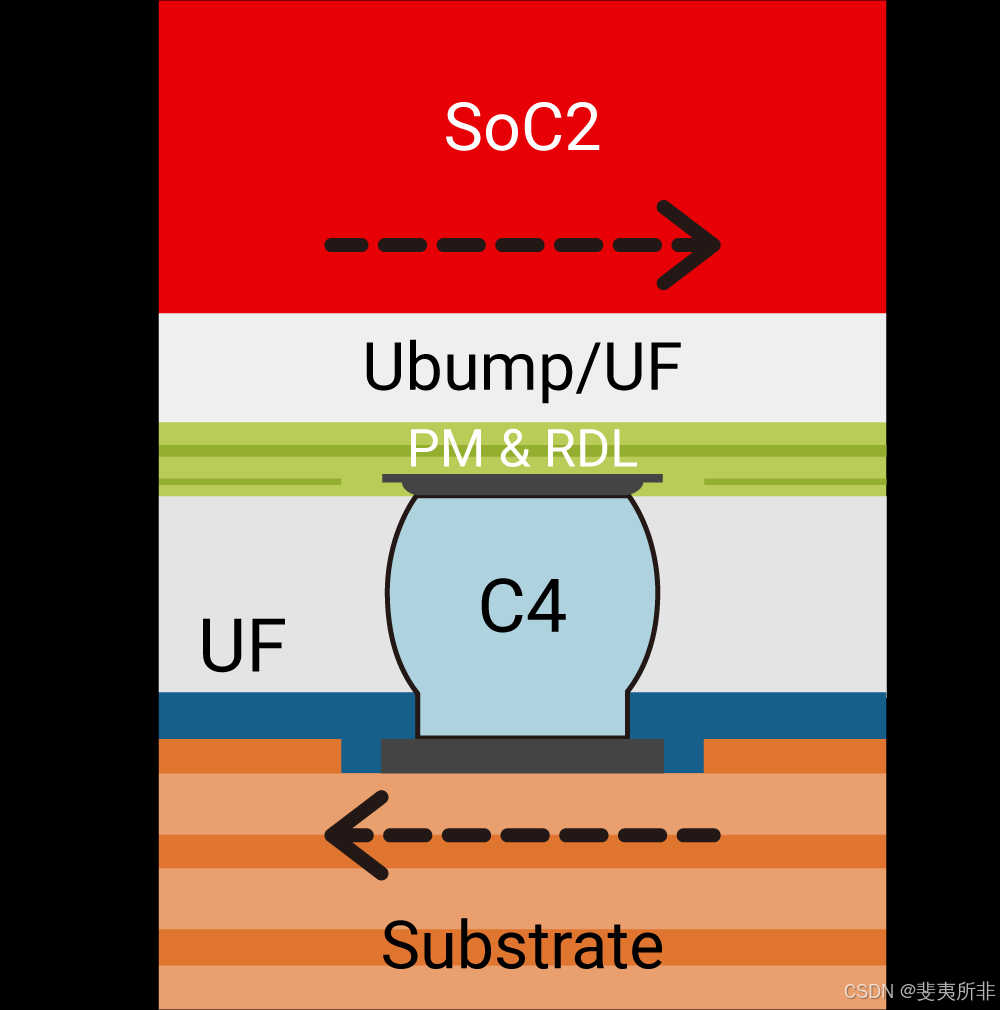

CoWoS®-R (Chip on Wafer on Substrate with silicon interposer with fan-out RDL interposer) is a member of CoWoS® advanced packaging family that leverages a redistribution layer (RDL) interposer as the interconnect between System on Chip (SoC) and/or high bandwidth memory (HBM) to achieve heterogeneous integration. An RDL interposer is comprised of polymer and copper traces and is relatively flexible. This enhances C4 joint integrity and allows the package to scale its size to meet very complex functional demands.

CoWoS-R®(衬底上晶圆上芯片,带有带扇出 RDL 中介层的硅中介层)是 CoWoS® 先进封装系列的成员,它利用再分布层(RDL)中介层作为片上系统(SoC)和/或高带宽内存(HBM)之间的互连,以实现异构集成。RDL 中介层由聚合物和铜走线组成,相对灵活。这增强了 C4 接头的完整性,并允许封装扩展其尺寸以满足非常复杂的功能需求。

Key CoWoS®-R features include:

CoWoS-R® 的主要功能包括:

-

An RDL interposer of up to 6 copper layers for routing with a minimum 4μm pitch (2μm line width/spacing).

多达 6 个铜层的 RDL 中介层,用于最小 4μm 间距(2μm 线宽/间距)的布线。 -

The RDL interconnect offers good signal and power integrity with a lower RC value routing line to achieve a high data transmission rate. The co-planar Ground-Signal-Ground-Signal-Ground (GSGSG) and interlayer ground shielding with six RDL interconnections offers superior electrical performance.

RDL 互连通过较低的 RC 值布线线路提供良好的信号和电源完整性,以实现高数据传输速率。共面接地-信号-接地-信号-接地(GSGSG)和层间接地屏蔽具有 6 个 RDL 互连,可提供卓越的电气性能。 -

RDL layer and C4/underfill (UF) layers provide an excellent buffer thanks to the coefficient of thermal expansion (CTE) mismatch between an SoC and the corresponding substrate. The strain energy density is greatly reduced in the C4 bump area.

由于 SoC 和相应基板之间的热膨胀系数(CTE)不匹配,RDL 层和 C4/底部填充(UF)层提供了出色的缓冲。C4 凸块区域的应变能密度大大降低。

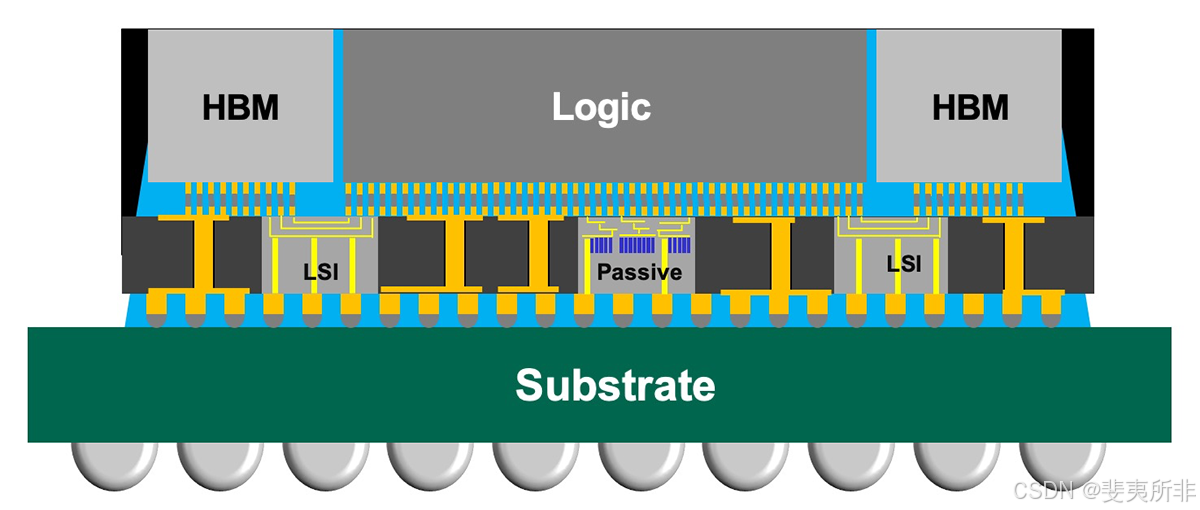

CoWoS®-L

CoWoS®-L is one of the chip-last packages on the CoWoS® (Chip on Wafer on Substrate) platform. It combines the merits of CoWoS®-S and InFO (Integrated Fan-Out) technologies to provide the most flexible integration using an interposer with a Local Silicon Interconnect (LSI) chip for die-to-die interconnect and RDL layers for power and signal delivery.

CoWoS-L® 是 CoWoS®(Chip on Wafer on Substrate)平台上的 Chip-Last 封装之一。它结合了 CoWoS-S® 和 InFO(集成扇出)技术的优点,使用中介层和本地硅互连(LSI)芯片进行晶粒间互连,并使用 RDL 层进行电源和信号传输,从而提供最灵活的集成。

Key CoWoS®-L features include:

CoWoS-L® 的主要功能包括:

- LSI chips for a high routing density die-to-die interconnect through multiple layers of sub-micron copper lines. LSI chips can feature a variety of connection architectures, e.g., System on Chip (SoC)-to-SoC, SoC-to-chiplet, SoC-to-High Bandwidth Memory, within each product, and can be used repeatedly in multiple products. The corresponding metal types, layer counts, and pitches align with the offering from CoWoS®-S.

LSI 芯片,用于通过多层亚微米铜线实现高布线密度 Die-to-Die 互连。LSI 芯片可以在每个产品中具有多种连接架构,例如片上系统(SoC)到 SoC、SoC 到 Chiplet、SoC 到高带宽内存,并且可以在多个产品中重复使用。相应的金属类型、层数和间距与 CoWoS-S® 的产品一致。 - A molding-based interposer with a wide pitch of RDL layers on the front-side, back-side and Through InFO Via (TIV) that delivers signal and power provides a low loss of high frequency signals during high-speed transmission.

一种基于成型的中介层,在正面、背面具有宽间距的 RDL 层,并通过 InFO Via(TIV)提供信号和功率,可在高速传输期间提供低高频信号损耗。 - The ability to integrate additional elements, such as stand-alone embedded Deep Trench Capacitors, underneath the SoC die to improve power management.

能够在 SoC 芯片下方集成其他元件,例如独立的嵌入式深沟槽电容器,以改善电源管理。

一文读懂先进封装 CoWoS

原创 大 K 向前冲 科技词话 2024 年 06 月 05 日 08:31 广东

CoWoS,全称为 Chip on Wafer on Substrate。该表述为芯片在晶圆上、在基板上的集成结构。该定义可概括为一类先进封装技术,其通过将多颗芯片进行堆叠并集成于同一基板之上,形成结构紧凑且运行高效的功能单元。

当前全球芯片制程工艺已进入 3 nm~5 nm 区间,逼近物理极限。先进制程芯片的设计难度、工艺复杂度与研发成本显著提升,摩尔定律演进速度放缓,半导体行业进入后摩尔时代。

前道、中道与后道工艺

在芯片制造体系中,前道、中道与后道为半导体生产流程中的三个主要阶段,各阶段内容如下:

前道(Front-End Manufacturing)

前道工艺以晶圆制造为主体,指在空白硅片上完成电路结构制备的过程,包含光刻、刻蚀、薄膜生长、离子注入、清洗、CMP(化学机械抛光)及量测等步骤。该阶段在硅片上形成晶体管、有源器件及多层互连结构。

中道(Middle-End Manufacturing)

中道为晶圆制造与封装测试之间的过渡环节,常被称为凸点制备工艺。该环节主要在晶圆表面制备凸点(Bumps),用于后续封装阶段实现芯片与外部电路的电气连接。随着高密度芯片需求的提升,中道工艺的重要性持续提升,在倒装芯片(Flip-Chip)技术中尤为突出。

后道(Back-End Manufacturing)

后道工艺以封装与测试为主体,包含减薄、划片、装片、引线键合、模塑、电镀、切筋/成型及最终测试等步骤。该阶段将圆形硅片分割为独立芯片,完成封装壳体成型,并通过电气测试验证产品性能是否满足规范。

上述三个阶段共同构成完整的半导体制造流程,各阶段工艺水平均影响最终产品的性能与质量。伴随技术发展,各阶段工艺路径与实现方式持续迭代。

CoWoS 封装工艺

当前集成电路前道制程工艺发展存在限制,同时大模型、AIGC 等新兴应用场景快速发展,产业界对芯片性能的需求持续提升。集成电路企业逐步转向后道先进封装工艺以实现产品性能提升,2.5D 封装、3D 封装均属于先进封装技术体系。

2.5D 封装

该封装形式将芯片置于中介层上方,通过微型金属互联结构实现多芯片间的信号连接与整合。

3D 封装

3D 封装技术实现芯片的垂直方向堆叠,可用于高性能逻辑芯片与 SoC(System on Chip)器件的制备。

行业内头部企业纷纷布局先进封装领域,市场竞争格局呈现集中化特征。后摩尔时代背景下,先进制程研发成本持续上升,晶圆代工企业的发展重心由纳米制程节点迭代转向封装技术创新。台积电、英特尔、三星、联电等芯片制造企业均涉足先进封装领域。全球范围内 6 家主要厂商承担超过 80% 的先进封装晶圆处理量,其中包括 2 家 IDM 厂商(英特尔、三星)、1 家晶圆代工厂商(台积电)及全球排名前三的封测厂商(日月光、Amkor、JCET)。

CoWoS 归属于 2.5D 先进封装技术,由 CoW 与 oS 两部分构成:先通过 Chip on Wafer(CoW)工艺将芯片与硅晶圆连接,再将 CoW 结构与基板(Substrate)集成,形成完整的 CoWoS 结构。该技术将多颗芯片集成于同一硅中介层,实现芯片间的高密度互联。台积电在硅中介层中采用微凸块(μBumps)、硅通孔(TSV)等结构替代传统引线键合,提升互联密度与数据传输带宽。CoWoS 技术可实现系统性能提升、功耗降低与封装体积缩小,为相关企业在封装技术领域建立竞争优势提供支撑。

CoWoS 的三种分类

依据所采用中介层(interposer)类型的差异,台积电将 CoWoS 封装技术划分为三类,分别为 CoWoS-S(Silicon Interposer)、CoWoS-R(RDL Interposer)与 CoWoS-L(Local Silicon Interconnect and RDL Interposer)。

CoWoS-S

CoWoS-S 为经典型 CoWoS 技术,采用硅中介层。该技术于 2011 年首次推出,是以硅(Si)衬底作为中介层的 chip-on-wafer-on-substrate 封装方案,可提供多种中介层尺寸、HBM 堆叠数量与封装尺寸,实现大于 2 倍光罩尺寸的集成规模,可将高性能 SoC 芯片与 4 颗及以上 HBM2/HBM2E 存储芯片集成。行业早期提及的 CoWoS 通常指代该类硅中介层型先进封装技术。

CoWoS-R(RDL Interposer)

CoWoS-R 采用有机基板与重新布线层(RDL)替代硅材料作为中介层。该技术基于 InFO 工艺,以 RDL 作为中介层实现 chiplet 之间的互联,适用于 HBM(高带宽存储器)与 SoC 的异构集成场景。RDL 中介层由聚合物材料与铜布线构成,具备较高的机械灵活性,可提升 C4 接头结构稳定性,并支持封装尺寸扩展以适配更复杂的功能需求。

CoWoS-L

CoWoS-L 采用小芯片(chiplet)与 RDL 作为中介层,融合 CoWoS-S 与 InFO 技术的特征,集成灵活性较高。该技术通过本地硅互连(LSI)芯片实现芯片间互联,并搭配 RDL 层完成电源与信号传输,初始集成规模为 1.5 倍光罩尺寸中介层与 1 颗 SoC 加 4 颗 HBM 芯片组合,可进一步扩展封装尺寸以实现更多芯片的集成。

CoWoS 是什么?台积电如何依托 CoWoS 形成全球竞争优势

原创 张海军 傅里叶的猫 2024 年 10 月 22 日 08:08 上海

CoWoS 为台积电旗下先进封装技术的专属标识。在本轮人工智能技术发展进程中,CoWoS 对产业演进形成支撑,该技术与高性能计算芯片及人工智能芯片的发展存在紧密关联。

CoWoS 的发展历程

CoWoS(Chip on Wafer on Substrate)技术的研发历程可追溯至约 15 年前,其启动背景为台积电对摩尔定律物理极限的前瞻性应对。

2009 年,台积电创始人张忠谋邀请蒋尚义回归公司。蒋尚义提出推进先进封装技术研发的规划,其判断依据为摩尔定律逐步逼近极限,半导体产业需探索新的技术发展路径。彼时台积电晶圆制造工艺向更小线宽节点演进,而传统封装工艺中的互联线宽未实现同步微缩,拓展封装技术领域可突破既有技术框架。

实验数据显示,采用传统封装方案会造成芯片间数据传输速率约 40% 的损耗,先进封装技术可对该性能损失进行补偿。蒋尚义的研发规划获得张忠谋支持,研发团队规模为 400 名工程师,项目资金投入为 1 亿美元,CoWoS 技术研发工作正式启动。

该技术初期因成本偏高,市场应用范围有限,仅 Xilinx 存在小批量采购需求。针对市场反馈,研发团队开展成本优化工作,推出改进型封装方案。该方案为后续与同行业企业竞争奠定技术基础。伴随高性能计算(HPC)与人工智能(AI)领域需求增长,CoWoS 凭借高集成度与综合性能优势,市场关注度持续提升。

CoWoS 技术原理与工艺流程

CoWoS 全称为 Chip on Wafer on Substrate,该技术通过硅中介层(Interposer)实现处理器、存储器等多颗芯片的集成,形成高性能封装系统。技术实现路径为:先通过 Chip on Wafer(CoW)工艺将芯片与硅晶圆互联,再将 CoW 结构与封装基板结合,形成完整的 CoWoS 体系。该架构通过硅中介层实现多芯片互联,可实现封装体积缩减、功耗降低与引脚数量减少。

CoWoS 封装工艺流程可划分为三个阶段,相关划分依据参考中国台湾大学公开资料。

第一阶段,裸片(Die)与中介层(Interposer)通过微凸块(μBump)实现键合,采用底部填充(Underfill)工艺对键合界面进行防护。

第二阶段,裸片与载板(Carrier)完成贴合。封装基板属于 PCB 技术分支,为半导体封测关键材料,具备高密度、高精度、小型化等特征,可实现芯片承载、散热、防护及芯片与母板间的电气互联。该阶段通过化学机械抛光(CMP)工艺完成中介层薄化处理,移除中介层冗余结构。

第三阶段,晶圆切割形成独立芯片,芯片与封装基板完成键合,加装封装保护环与盖板,采用热界面材料(TIM)填充接合间隙。

从功能层面概括,CoWoS 技术可缩短芯片间物理间距,提升芯片间数据交互效率。该架构可类比为高密度建筑群间的立体互联通道,相较于独立分布的芯片布局,互联效率存在显著提升。

封装技术体系演进

芯片封装技术沿 2D 向 3D 方向迭代,衍生出多种技术路线。迭代过程中出现系统级封装(SiP)等集成方案,主流技术类型包括 2.5D 封装(Interposer、RDL)、3D 封装(TSV)、倒装芯片(Flip Chip)、凸点(Bumping)、晶圆级封装(WLP)、CoWoS、InFO(Integrated Fan-Out)、EMIB(Embedded Multi-die Interconnect Bridge)等。

CoWoS 属于 2.5D 异构多芯片封装技术。2.5D 封装架构中,芯片平行布置于中介层上方,通过微凸块(μBump)与中介层布线实现芯片间互联;中介层通过硅通孔(TSV)实现层间互联,再通过 C4 锡球与传统 2D 封装基板键合。该架构可提升系统集成度,支持芯片间高速数据传输与资源共享。

依据日月光(ASE)公开资料,2.5D 封装具备以下特征:布线密度可达 L/S 0.4/0.4 μm,I/O 密度大于 400 μbumps/mm² 且具备间距扩展能力,支持同构/异构存储器、光电器件集成,可嵌入去耦电容或有源器件,封装可靠性表现优异。该技术广泛应用于高性能计算、人工智能、网络通信等领域,常与高带宽内存(HBM)模块搭配使用。

CoWoS 封装技术分类

台积电针对不同应用场景,将 CoWoS 划分为三类技术分支,分别对应硅中介层(Si Interposer)、重布线层(RDL)与局部硅互联(LSI)方案。

CoWoS-R

CoWoS-R 基于 InFO 技术,采用 RDL 中介层实现 chiplet 间互联,主要应用于 HBM 与 SoC 异构集成场景。RDL 中介层由聚合物基材与铜布线构成,具备机械柔性,可适配封装尺寸扩展需求。

CoWoS-R 技术特征如下:

- RDL 中介层可实现最多 6 层铜布线,最小线宽/间距为 2 μm/2 μm;

- 互联结构具备良好的信号完整性与电源完整性,低 RC 延时可支持高速数据传输,共面与层间接地屏蔽结构可提升电气性能;

- RDL 层与 C4/底部填充层可缓冲 SoC 与基板间的热膨胀系数(CTE)失配,降低 C4 凸块应力。

CoWoS-S

CoWoS-S 为当前主流技术方案,采用硅中介层架构。依据台积电官网信息,该平台可为高性能计算应用提供集成能力,支持多种中介层尺寸、HBM 堆叠数量与封装规格,可实现大于 2 倍光罩尺寸(约 1700 mm²)的中介层集成,可将高端 SoC 芯片与 4 颗及以上 HBM2/HBM2E 存储芯片进行整合。

CoWoS-L

CoWoS-L 融合 CoWoS-S 与 InFO 技术特征,集成灵活性较高。该方案通过局部硅互联(LSI)实现芯片间互联,采用 RDL 层完成电源与信号传输,可进一步扩展封装尺寸以适配更多芯片集成需求。其优势包括支持高速低损耗高频信号传输,可在 SoC 下方集成额外元器件。

第 5 代 CoWoS 技术(CoWoS-S5)

台积电于 2021 年发布第 5 代 CoWoS 技术,产品综合性能实现显著提升。CoWoS-S5 将中介层尺寸扩展至 3 倍光罩极限(2500 mm²),可在单中介层上集成 3 颗及以上逻辑芯片与 8 颗 HBM 存储芯片。相较于前代方案,该代技术可实现晶体管集成数量近 20 倍提升,内存堆叠数量由 4 颗提升至 8 颗。

CoWoS-S5 采用新型硅通孔(TSV)方案,扩大中介层面积并采用加厚铜互联线,进一步优化电气与热性能。该技术通过 4 片全幅光罩拼接与 RDL 工艺实现互联区域连续性,引入新型金属堆叠与亚微米双镶嵌结构,改善信号完整性。HBM2E 存储芯片在该代中介层上完成验证,数据传输速率达 3.2 GT/s,后续可兼容 HBM3 标准,速率提升至 4 GT/s。

CoWoS-S5 采用 5 层超低电阻互联金属方案,金属线电阻与通孔接触电阻降低 50% 以上,最小线宽/间距维持亚微米级别,满足高密度布线要求。该方案通过电迁移(EM)、应力迁移(SM)与时间相关介质击穿(TDDB)可靠性测试,无性能衰减现象。

针对高频信号传输损耗问题,CoWoS-S5 完成 TSV 结构重新设计,插入损耗(S21)指标优化,信号完整性得到提升。

热管理方面,CoWoS-S5 提供两种封装方案:

- 环型封装:裸片背面外露,可直接与散热器接触;

- 盖型封装:通过热界面材料(TIM)实现芯片与盖板间的热传导。

该代技术采用新型非凝胶型 TIM,热导率大于 20 W/K,覆盖率达 100%,经 TCG1000x、uHAST264h 与 TSAM 测试后热阻衰减小于 10%,可满足高性能计算与人工智能芯片的高功率散热需求。

文中部分内容参考自甬兴证券《CoWoS 技术引领先进封装,国内 OSAT 有望受益》

先进制程,谁最有话语权?

原创 寄语 头部科技 2024 年 10 月 31 日 19:20 北京

文丨寄语

人工智能产业发展进程中,行业竞争的焦点集中于先进制程领域,先进封装为该体系中的重要组成环节。

Blackwell 芯片采用台积电 4 nm 工艺制造,集成晶体管数量达 2080 亿个,较前代 H100 芯片的 800 亿个晶体管实现显著提升。

Blackwell 架构具备更高的运算能力,同时对芯片制造工艺与封装技术提出更高要求。

本文围绕 Blackwell 芯片所依赖的 CoWoS 先进封装技术展开阐述,并对比同类竞争技术的发展态势。

先进封装领域的技术布局与产能供给,对产业格局形成直接影响。

CoWoS 技术概述

台积电总裁魏哲家在业绩说明中提及,CoWoS 先进封装产能持续处于紧张状态,企业正推进对应产能的扩充工作。

CoWoS(Chip on Wafer on Substrate)为台积电推出的先进封装技术,主要应用于高性能计算(HPC)与人工智能(AI)器件制造。

该技术属于高端系统级封装(SiP)方案,相较于传统多芯片模块(MCM),可在紧凑布局内实现多芯片并排集成。

CoWoS 归属于 2.5D 先进封装技术,由 CoW(Chip on Wafer)与 oS(Wafer on Substrate)两部分构成,通过硅中介层实现多芯片集成,形成高性能封装系统。

2.5D 封装采用芯片水平堆叠形式,将系统单芯片(SoC)与高带宽内存(HBM)布置于中介层之上,通过微凸块(micro bump)实现连接,依托中介层内部金属布线完成 SoC 与 HBM 之间的电气连接与信号传输。中介层通过硅通孔(Through-Silicon Via, TSV)技术与下方 PCB 基板相连,实现多芯片一体化封装,具备体积小、功耗低、引脚数量少、成本可控等特征。

2.5D 与 3D 封装技术对比

3D 封装采用芯片垂直堆叠架构,通过硅通孔实现垂直方向上不同芯片间的信号传输,可降低信号延迟。该技术在设计体系、量产能力与供应链配套方面尚未成熟,受成本因素制约,当前行业主流方案仍为 2.5D 封装。

CoWoS 技术将多颗芯片集成于同一硅中介层,实现芯片间的高密度互联。

台积电在硅中介层中采用微凸块(μBumps)、硅通孔(TSV)等结构替代传统引线键合,提升互联密度与数据传输带宽。

多颗有源硅芯片通常包含逻辑芯片与 HBM 堆栈,集成于无源硅中介层之上。中介层承担顶部有源芯片间的通信传输功能,整体结构再与搭载 I/O 端口的封装基板连接,适配系统 PCB 应用场景。

CoWoS 技术可实现系统性能提升、功耗降低与封装尺寸缩小,支撑台积电在先进封装领域建立竞争优势。

台积电披露,其先进封装产能缺口呈持续扩大趋势。

台积电将 CoWoS 前段关键 CoW 制程与后段 WoS 制程委外至日月光投控旗下矽品精密与 Amkor(安靠)承接。

日月光、安靠等企业承接台积电外溢订单,对其 2024 年度经营业绩形成正向支撑。

CoWoS 技术分类

依据所采用中介层类型的差异,台积电将 CoWoS 封装技术划分为三类,分别为 CoWoS-S(Silicon Interposer)、CoWoS-R(RDL Interposer)与 CoWoS-L(Local Silicon Interconnect and RDL Interposer)。

CoWoS-S 封装

CoWoS-S 为经典型 CoWoS 技术,采用硅基板作为中介层。单片硅中介层在量产过程中存在良率控制相关问题。

CoWoS-R 封装

CoWoS-R 采用有机基板/重新布线层(RDL)替代硅材料作为中介层。有机中介层以细间距 RDL 为主体结构,具备机械柔性,可作为应力缓冲结构,缓解基板与中介层之间热膨胀系数失配引发的可靠性问题。该技术可在 HBM 与芯片、芯片与基板之间提供高速连接通道,相较于 CoWoS-S,在可靠性与良率方面表现更优。

CoWoS-L 封装

CoWoS-L 面向高端产品扩展需求构建新型架构,采用局部硅互连(LSI)与 RDL 中介层组成重组中介层(RI),融合 CoWoS-S 与 InFO 技术特征,缓解 CoWoS-S 采用大尺寸硅中介层带来的良率问题。

部分实现方案中,CoWoS-L 采用绝缘体通孔(TIV)替代 TSV,降低信号插入损耗。该架构集成灵活性突出,为英伟达新一代 Blackwell 超级芯片所采用的关键技术。

标准 CoWoS 工艺中,已知合格裸片(KGD)的 SoC 芯片与 HBM 芯片通过间距 30~60 μm 的微凸块并排集成于硅中介层晶圆之上。

硅中介层在晶圆厂阶段完成多层互连、TSV 与 eDTC 结构预制,再依据中介层尺寸将 CoW 晶圆切割为独立模块,与封装基板组装形成系统级封装(SiP)。

在顶层芯片与基板之间引入硅中介层,可实现更精细的互联间距与更短的水平传输路径,优化信号完整性(SI)与电源完整性(PI)。

CoWoS-L 封装架构

CoWoS-L 封装由顶层芯片、重组中介层与基板三部分构成。

顶层芯片通过细间距微凸块与中介层键合,中介层承担顶层芯片承载功能并构成 CoW 结构,LSI 芯片承担芯片间通信的主要传输与交互功能。

中介层上下两面均布设 RDL 层,分别适配微凸块与 C4 凸块布线需求。

模塑化合物包围的 TIV 结构提供从基板至顶层芯片的垂直传输通道,信号插入损耗较低。

最终将 CoW 芯片与基板键合,完成 CoWoS-L 封装流程。

CoWoS-L 集成 LSI-1 与 LSI-2 独特架构,为单一封装内 SoC 间互联与 SoC-HBM 互联提供设计灵活性。

TIV 结构在超高速数据传输场景下具备信号与电源完整性优势,可规避 TSV 带来的插入损耗问题。

eDTC 小芯片架构在相同缺陷密度的晶圆工艺条件下具备更高利用效率。可靠性测试数据表明,CoWoS-L 具备稳定的量产可行性。

CoWoS-L 具备异构集成能力,可适配高性能计算与人工智能领域的需求升级。

台积电与海力士协同发展,构建产业优势

CoWoS 技术研发始于 2011 年,台积电为构建竞争优势,与海力士开展战略合作。台积电在逻辑芯片领域具备技术积累,海力士在存储芯片领域拥有产业资源,双方形成互补格局。

双方整合技术优势,共同构建 CoWoS 架构,实现逻辑芯片与存储芯片的协同集成。

该合作推动海力士完成 HBM(High Bandwidth Memory,高带宽内存)技术迭代,使其在高端存储市场建立竞争壁垒。

双方合作形成技术护城河,导致三星直至 2024 年 7 月才通过英伟达 HBM3 认证,错失人工智能产业发展机遇期。

海力士在 HBM3 产品领域市场占有率超过 90%,领先于传统存储企业三星。

台积电 CoWoS 封装技术搭配海力士 HBM 存储芯片,成为英伟达高端 AI 芯片的主流方案。

HBM 高焊盘数量与短布线长度需求,依赖 CoWoS 这类 2.5D 先进封装技术实现高密度短距连接,该连接无法通过传统 PCB 或封装基板实现。

CoWoS 以可控成本实现高互联密度与大封装尺寸,成为 HBM 系统的主流封装载体。

当前主流人工智能加速器均采用 HBM 架构,数据中心高端 GPU 产品大多采用台积电 CoWoS 封装方案。

英特尔先进封装技术布局

英特尔在先进封装领域持续投入,封装技术为企业战略布局的重要方向。与部分企业采用委外封装模式不同,英特尔构建自主封装体系,覆盖芯片研发、制造与应用全流程。

英特尔在先进制程领域与台积电存在差距,但在先进封装领域技术水平接近台积电。

英特尔对标 CoWoS 的 2.5D 封装技术为 EMIB,该技术于 2017 年实现商用,应用于 Sapphire Rapid 数据中心处理器。

英特尔第一代 3D IC 封装技术为 Foveros,2019 年应用于 Lakefield 计算处理器。

EMIB 技术通过埋置于基板内的硅桥(Silicon Bridge)连接 HBM 存储芯片与运算芯片,实现芯片间直连,提升器件能效。

Foveros 技术采用 3D 堆叠架构,将存储、运算等不同功能芯片垂直堆叠,通过铜质穿透结构实现层间连接。

2022 年,英特尔推出 Co-EMIB 技术,实现 2.5D 与 3D 封装技术融合,可实现多颗 Foveros 单元互联,性能接近单芯片水平。该技术支撑英特尔推出 Ponte Vecchio 处理器,面向高性能计算市场。

Ponte Vecchio 集成 11 个硅桥、47 个有源裸片、5 种工艺节点,晶体管数量超 1000 亿个(不含 HBM),封装内包含三倍于传统光罩尺寸的硅片,为行业内复杂度较高的集成封装方案。

英特尔先进封装技术在性能与原理上与台积电方案接近,企业试图切入英伟达高端芯片封装供应链。

行业观点认为,英特尔封装方案成本偏高,价格竞争力不足。

半导体工艺发展趋势

半导体工艺技术在数十年间持续迭代,光刻技术已进入 EUV 时代,制程间距不断缩小。

光刻技术、器件架构、新材料体系与集成方案的进步,推动器件在功耗、性能与面积(PPA)指标上持续优化。

CoWoS 技术的迭代为人工智能产业发展提供支撑,与高端 AI 芯片的规模化应用存在关联。

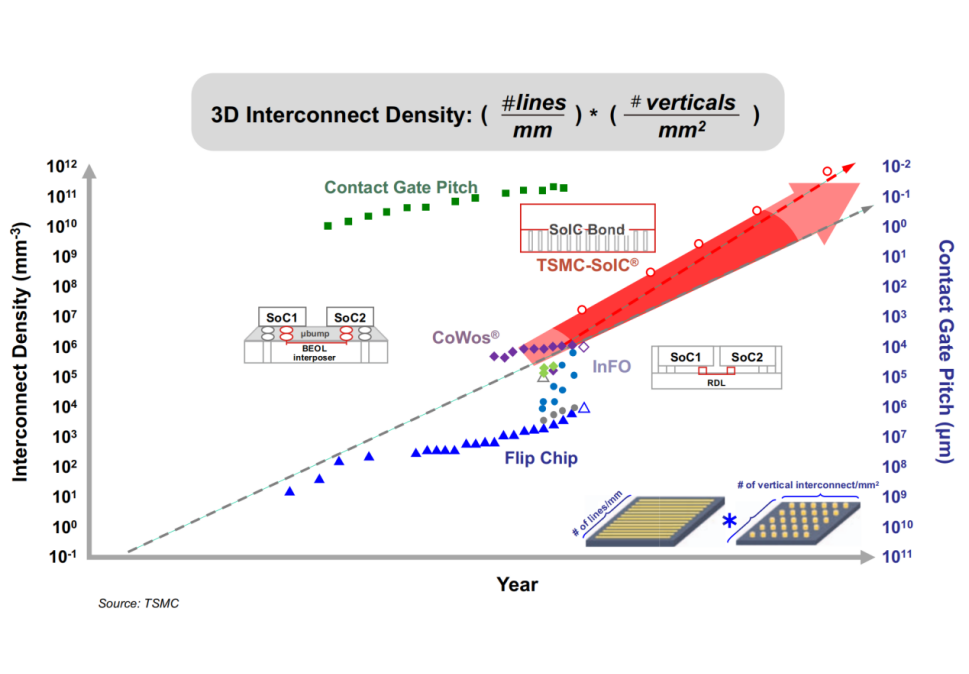

封装内部芯片间互联密度持续提升,CoWoS、InFO、SoIC 等集成方案不断缩小芯片间互联间距,可将 3D 互联密度提升多个数量级,支持封装系统集成超过 5000 亿个晶体管。

3D SoIC 与 CoWoS 技术支撑 AMD MI300X 加速器实现量产,该产品晶体管数量达 1530 亿个。

MI300X 产品推动 AMD 在人工智能芯片市场形成竞争力。

先进封装集成技术可提升数据传输速率、降低信号延迟、优化功耗表现,提升计算系统整体性能。

新型半导体器件开发过程中,晶圆制造工艺与封装技术均为重点投资方向。

AMD 与英特尔均采用 Chiplet 与 3D 封装技术路线,英伟达在人工智能芯片市场占据主导地位,同时面临市场竞争压力。

半导体产业创新持续推进,先进封装领域的技术竞争格局仍存在变动空间。

via:

-

CoWos 是什么?台积电是如何凭借 CoWos 独霸世界?原创 张海军 傅里叶的猫 2024 年 10 月 22 日 08:08 上海

https://mp.weixin.qq.com/s/Nt5HgXorXFa4of_sMhShnA -

一文读懂先进封装 CoWoS 原创 大 K 向前冲 科技词话 2024 年 06 月 05 日 08:31 广东

https://mp.weixin.qq.com/s/iB1TlR1-JXq7PUXP9cqF2A -

先进封装,供不应求! 原创 寄语 头部科技 2024 年 10 月 31 日 19:20 北京

https://mp.weixin.qq.com/s/q1kU1C042s0nI1Kxmwo53Q

—

-

CoWoS® - Taiwan Semiconductor Manufacturing Company Limited

https://3dfabric.tsmc.com/english/dedicatedFoundry/technology/cowos.htm -

CoWoS Capacity Set to Skyrocket by 2026: Massive Growth in Advanced Packaging | 2024

https://semiwiki.com/forum/index.php?threads/cowos-capacity-set-to-skyrocket-by-2026-massive-growth-in-advanced-packaging.21773/ -

PowerPoint Presentation - advanced-packaging_ssi_2023_yole_sch_updated-1.pdf

https://medias.yolegroup.com/uploads/2023/04/advanced-packaging_ssi_2023_yole_sch_updated-1.pdf -

CoWoS Packaging Technology: A Comprehensive Guide 2024

https://www.diskmfr.com/cowos-packaging-technology-a-comprehensive-guide/ -

An In-Depth Explanation of Advanced Packaging Technology: CoWoS | TrendForce News

https://www.trendforce.com/news/2023/08/08/an-in-depth-explanation-of-advanced-packaging-technology-cowos/ -

TSMC ‘Super Carrier’ CoWoS interposer gets bigger, enabling massive AI chips to reach 9-reticle sizes with 12 HBM4 stacks | 2023

https://www.tomshardware.com/tech-industry/tsmc-super-carrier-cowos-interposer-gets-bigger-enabling-massive-ai-chips-to-reach-9-reticle-sizes-with-12-hbm4-stacks -

GitHub - mikeroyal/CoWoS-Guide: Chip on Wafer on Substrate (CoWoS) Guide

https://github.com/mikeroyal/CoWoS-Guide -

Advanced Technology Leadership - 2021 HotChips TSMC Packaging Technologies for Chiplets and 3D_0819 publish_public.pdf

https://www.hc33.hotchips.org/assets/program/tutorials/2021 HotChips TSMC Packaging Technologies for Chiplets and 3D_0819 publish_public.pdf -

Understanding CoWoS Packaging Technology - AnySilicon

https://anysilicon.com/cowos-package/

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)