文献阅读(178)chiplet成本

文章目录题目:Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration时间:2022会有:DAC研究机构:清华马恺声本篇论文的主要贡献: 针对chiplet成本的量化分析模型以及分析方法chiplet确实可以提高芯粒良率,但同时也会增加其他的成本,包括基板、D2D开销以及NRE成本,本

- 题目:Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration

- 时间:2022

- 会有:DAC

- 研究机构:清华马恺声

- 参考链接:

本篇论文的主要贡献: 针对chiplet成本的量化分析模型以及分析方法

chiplet确实可以提高芯粒良率,但同时也会增加其他的成本,包括基板、D2D开销以及NRE成本,本篇论文便是首次分析了D2D的间接费用以及NRE成本

方法

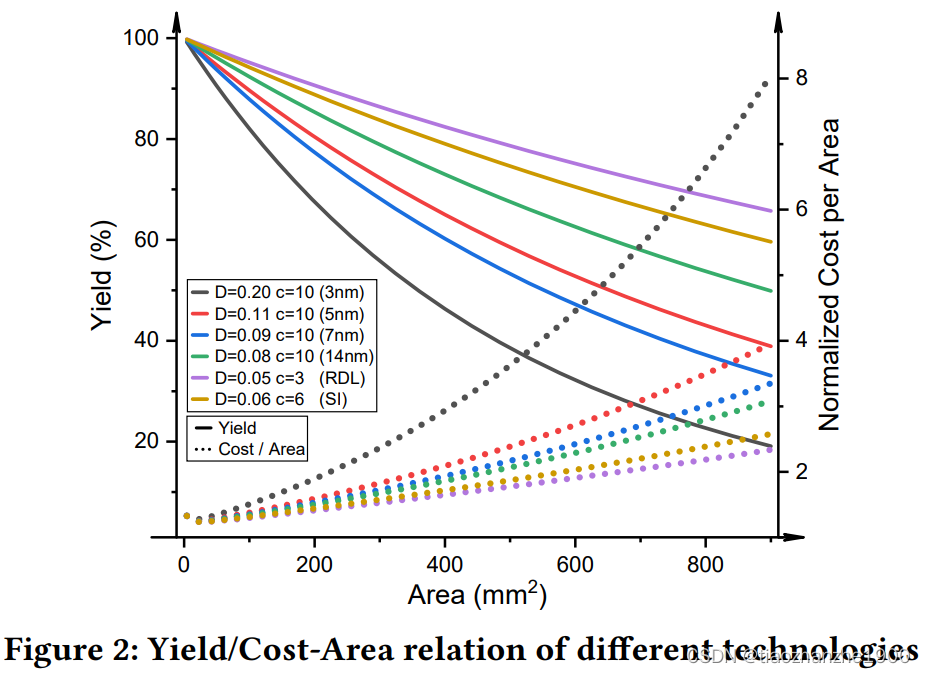

良率模型:

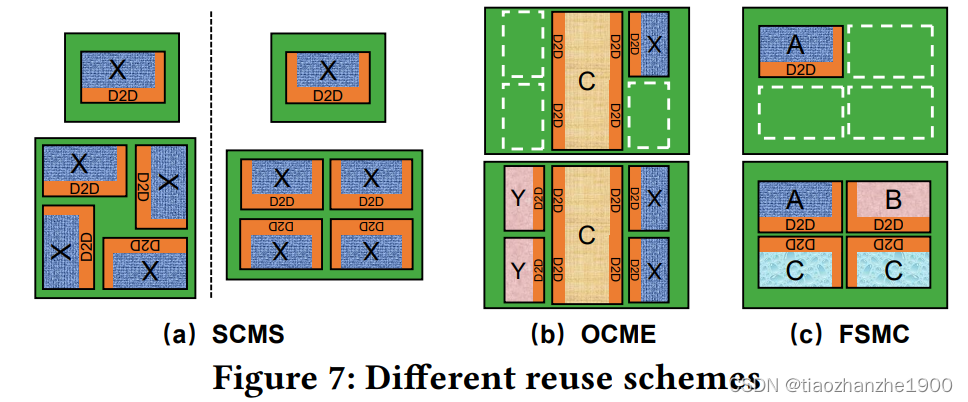

chiplet复用方式可以分为三类:

- 单芯片多系统(SCMS):完全同构的情况,显然NRE成本会减少很多

- 一中心多拓展(OCME)

- 固定插座多组合(FSMC)

实验

数据来源: commercial databases、public information

如何验证模型准确? 带入AMD的zen3架构的参数,MCM节省的成本最多可达50%,与AMD声称的一致

The comparison shows die costs result similar with AMD. Multi-chip integration can save up to 50% of the die cost.

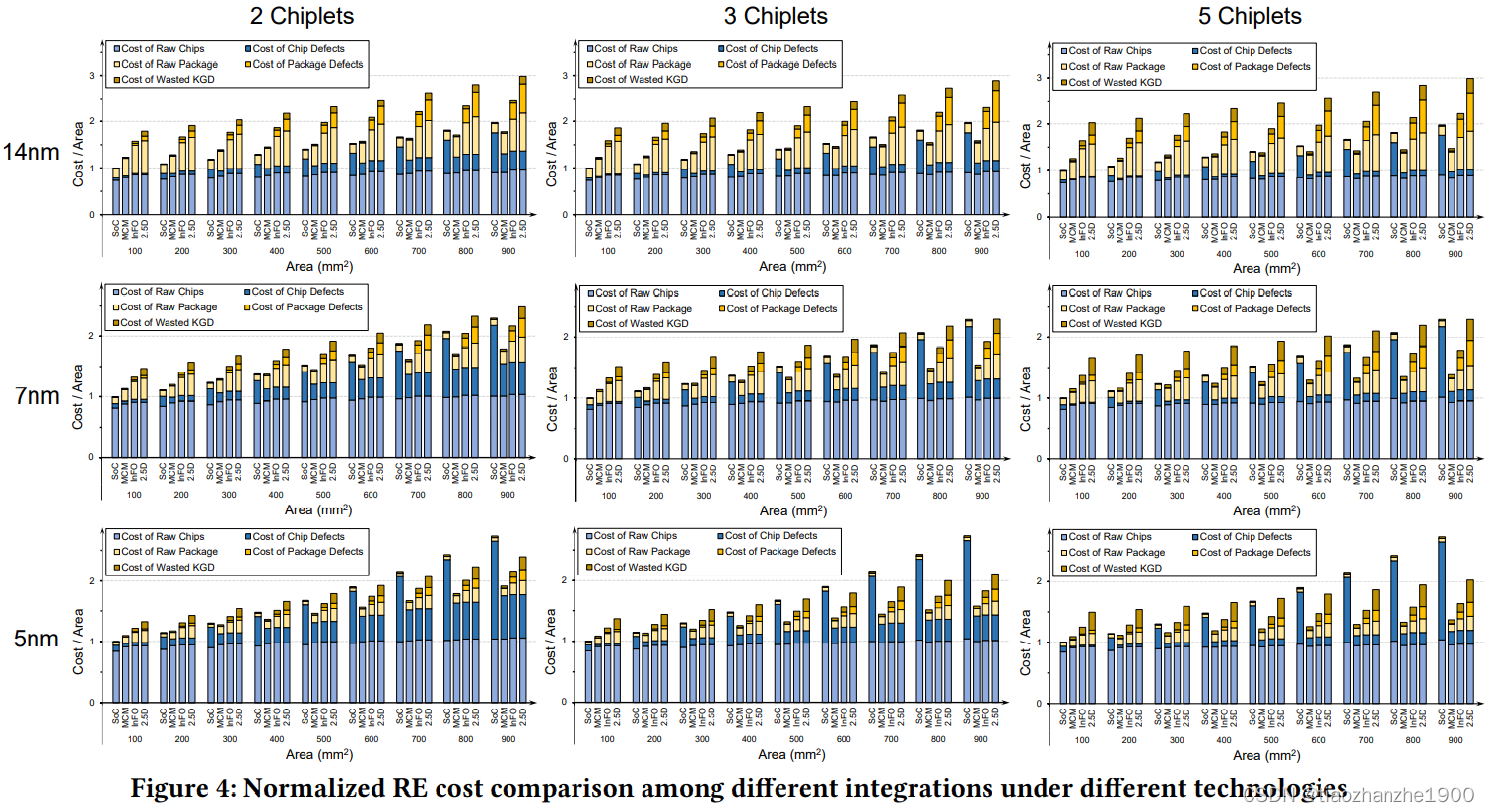

上图横坐标是不同工艺与不同芯片面积,纵坐标是单位面积的成本。其中成本主要考虑了RE Cost(recurring engineering cost,可以理解成不考虑一次性投入,生产一片芯片的钱),包括

- cost of raw chips

- cost of chip defects

- cost of raw package

- cost of package defects

- cost of wasted KGD(known good dies)

显然,芯片面积越大,chip defects带来的成本就更高;随着chiplet封装工艺的提升,raw package和packaging defects的成本也就越高。

结论:

- 工艺制程不够先进的,没必要做Chiplet

- 芯片面积不够大的,没必要做chiplet

- 5nm800mm2面积的SoC中,chip defects导致的额外成本占总制造成本的50%以上

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)