EMI 和 SI 的 PCB 设计技巧(第 1 部分)

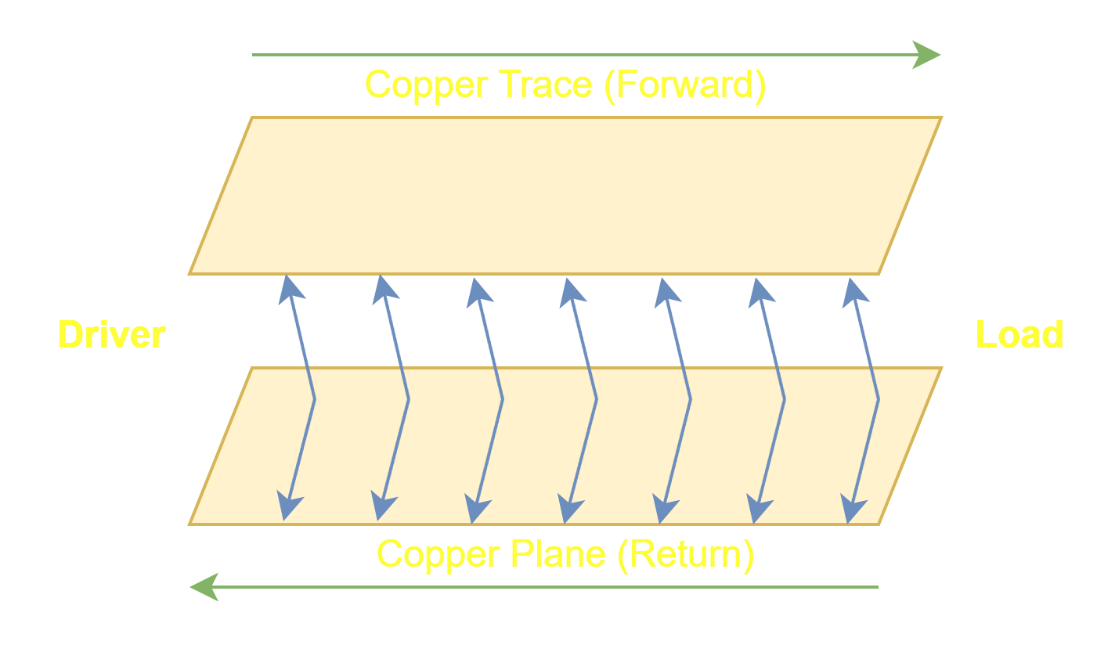

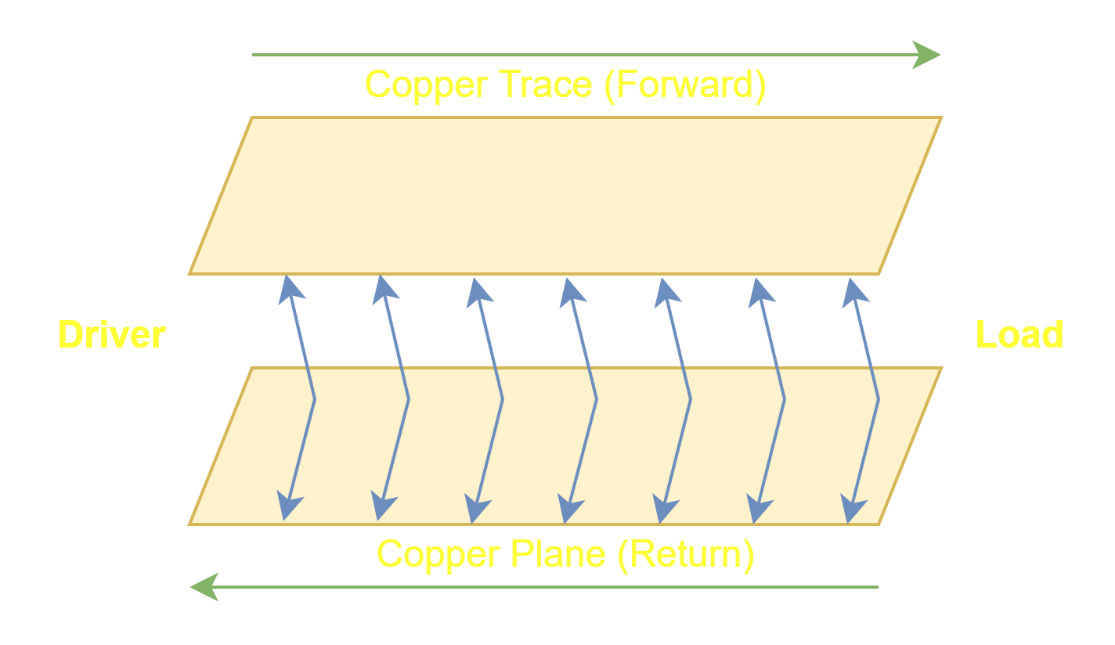

但是,我们需要小心,因为 IBIS 模型指定上升和下降时间为 20% 到 80%,而我们定义信号带宽时使用的是 10% 到 90% 的上升和下降时间!场中包含的信号能量在构成正向路径的走线与构成返回路径的走线下方的适当铜平面之间的介电空间中传播。在设计 PCB 时,考虑 EMI 和 SI 以及包含场时,关键是考虑电场和磁场,而不是考虑铜中的电子流。通常,如今我们处于数字领域,依靠方波来传输数据。第

在这两部分系列文章中,我们将介绍 PCB 布线和布局的基本原则和方法,以尽量减少出现 EMI 问题的可能性并保持适当的信号完整性。

第一篇文章概述了信号、能量和场的基础知识,以及数字领域的上升和下降时间,以及这对我们 PCB 设计师的意义。

信号、能量和场

核心要点以及很多人在电子和 PCB 设计中没有意识到的是,电场和磁场包含信号的全部能量。

大多数人认为能量在铜中传播,例如信号走线或返回平面 - 但事实并非如此!场中包含的信号能量在构成正向路径的走线与构成返回路径的走线下方的适当铜平面之间的介电空间中传播。

正向和返回路径,因此平面或迹线必须始终明确定义,以保持适当的信号完整性和 EMI。本质上,人们可以认为铜只是充当场的波导。

微带线和带状线

微带线(来源:Rick Hartley)

带状线(来源:Rick Hartley)

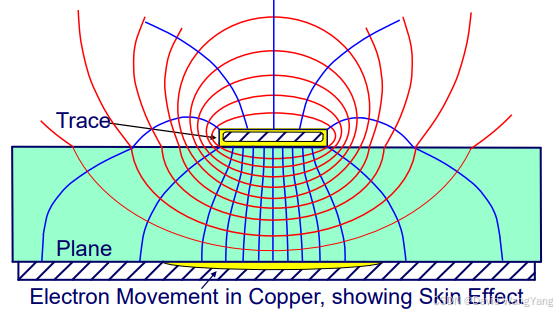

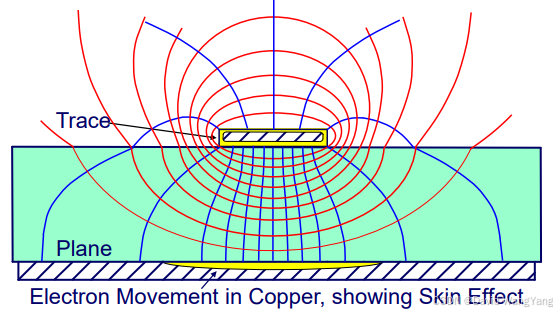

以下是 PCB 中电场和磁场的简单图示,如微带线和带状线所示。对于微带线迹(未埋入介电材料中的外层线迹),我们基本上将空气作为第一介电体,然后是下方 PCB 的介电体。电场(蓝色)和磁场(红色)分布相当广泛。

另一方面,在右侧图像中,带状线迹线显示场得到了更好的控制,因为我们在迹线顶部和中间下方有参考平面。简单地说,电磁场喜欢附着在这些返回或参考平面上 - 对于带状线迹线来说,现在得到了更好的控制。

在设计 PCB 时,考虑 EMI 和 SI 以及包含场时,关键是考虑电场和磁场,而不是考虑铜中的电子流。适当的 EMI 和 SI 性能基本上就是这一切的目的。

数字域中的频率

另一个误解是数字域中的频率。例如,许多人认为设计中信号(例如微控制器)的最高时钟频率是该系统中关注的最高频率。这与事实相去甚远!

通常,如今我们处于数字领域,依靠方波来传输数据。当然,这些方波并不是理想的——它们更接近梯形,因为我们有有限的边沿速率(上升和下降时间)。这些方波的基本周期可能是我们的时钟频率,例如微控制器的 8 或 16 MHz 时钟信号。问题是,我们不需要只关注这个基本时钟周期——我们还需要关注边沿转换!

这些边沿包含大部分信号能量和频率内容,而不是基本时钟周期。考虑到这些上升沿和下降沿,所关注的最高频率可以通过方波的傅里叶级数来确定。

通常,我们不需要花费那么多精力,只要给定 ns 内的上升/下降时间(10% 到 90%),我们就可以推导出一个简单的近似值,给出 GHz 内的信号带宽:

fmax=0.5t(上升/下降,ns)GHz

我们使用上升时间或下降时间,取决于哪个时间最快。

查找上升和下降时间

这是一个很棒且简单的近似值 - 但问题是我们如何才能算出 IC 的上升和下降时间?通常从数据表中无法完全看出这些信息。如果列出了上升和下降时间,它们通常是最佳情况(对应于最慢的上升和下降时间)。然而,它们并没有给出最小值,这反过来会导致非常高的带宽。

无论如何,我们都应该努力为最坏的情况进行设计——所以我们需要深入挖掘来找到这些上升和下降时间。

幸运的是,大多数制造商都为他们的 IC 提供 IBIS 文件。IBIS 文件通常用于模拟,我们也可以从中提取上升和下降时间。从 IC 制造商的网站下载 IBIS 文件后,打开它,然后查找 RAMP 部分。

RAMP 部分列出了两个参数:dv/dtr 和 dv/dtf。您可能已经猜到了,它们分别代表上升和下降率(电压变化/时间变化)。但是,我们需要小心,因为 IBIS 模型指定上升和下降时间为 20% 到 80%,而我们定义信号带宽时使用的是 10% 到 90% 的上升和下降时间!

请记住,这些数字也适用于特定负载(通常连接 50 欧姆负载,您的系统当然可能会有所不同)。

对于 ATMEGA328P(一种非常常见的微控制器),IBIS 文件中给出的最坏情况上升/下降时间为 0.76ns。通过线性缩放(大约乘以 1.3)将其从 20%-80% 转换为 10%-90% 的值,我们得出上升/下降时间略大于 1ns。

这意味着什么?

将此值代入我们的带宽近似公式,我们得出带宽为 500MHz!

这真是令人震惊,因为我们最初以为我们正在使用 10 MHz 范围内的“慢速”微控制器。所有频率内容都隐藏在这些上升沿和下降沿中(可以这么说)。

由此可见,当我们的走线长度开始看起来像分布式元件而不是集中元件时,我们需要小心(考虑:受控阻抗、反射等)。这意味着走线长度开始与最高频率分量的波长相当。

在 32MHz 下,对于微带线迹来说,这个长度约为 25cm。但是,在 500Mhz 下,我们需要注意线迹长度短至 17mm!

此外,快速边沿通常会产生更多辐射 - 因此比上升和下降时间较长的信号更容易引起 EMI 问题。

控制场并识别具有快速边沿的信号 - 然后控制其走线 - 是成功设计 PCB 以应对 EMI 和 SI 的基本要素和关键方面。

更多推荐

已为社区贡献2条内容

已为社区贡献2条内容

所有评论(0)